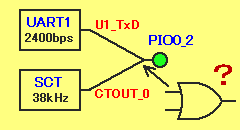

To drive Ir-LED with 38kHz modulation, original IrT uses 2 pins,

one for ANODE and the other for CATHODE.

|

|

/* * misc logic signal tricks by LPC810 * by uratan! 2014.11.14 * revised: 2016.09.04 */

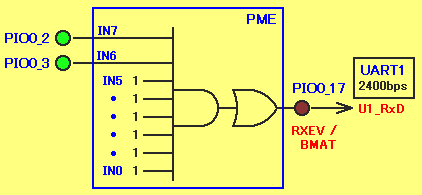

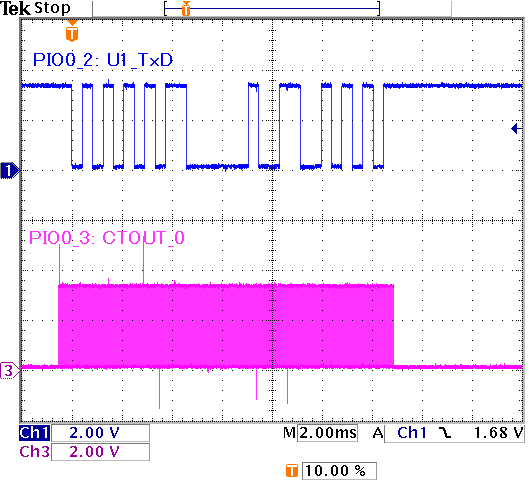

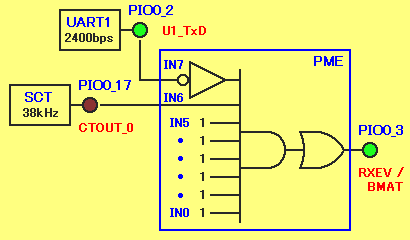

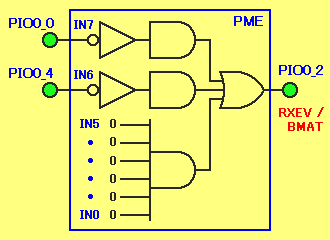

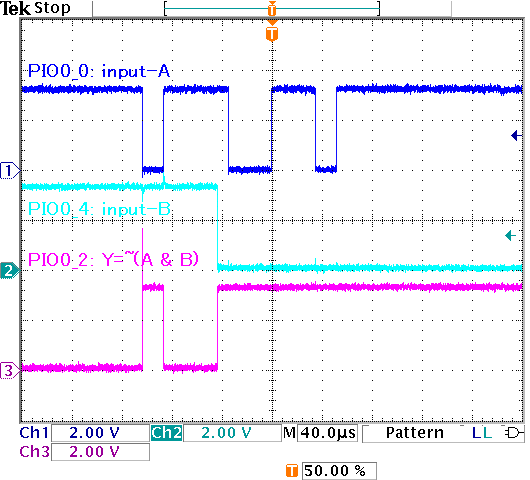

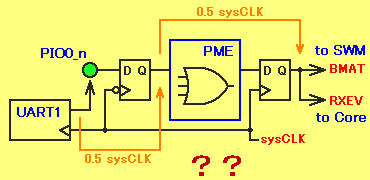

LPC810 has some interesting peripheral - Pattern Match Engine.

I can handle misc logic signal calculation with it, without any CPU actions.

get misc resources from:

patch for this experiment: tricks.diff.txt

base firmware: irt-06.zip

circuit diagram: my60clock-17.png

(about IrT and my 60-LED clock: 60clock.html)

To drive Ir-LED with 38kHz modulation, original IrT uses 2 pins,

one for ANODE and the other for CATHODE.

--- I may use internal port which does not have real pins to connect peripheral signals.

(except PIO0_10/11 which are true open-drain pins, never be high.)

(NXP says: do not recommend...)

--- I may use another internal port for U1_TxD if raw U1_TxD is not needed outside of the chip.

- * - * -

--- It seems that output signals are simply ORed with SWM by overwrapping assignment.

(But the User Manual says - DO NOT USE !)

- * - * -

--- After power-up/RESET, it takes a little time to function this,

but you can use more inputs or misc options below.

pull-UP/down Rs

input hysteresis / glitch filter

open-drain output

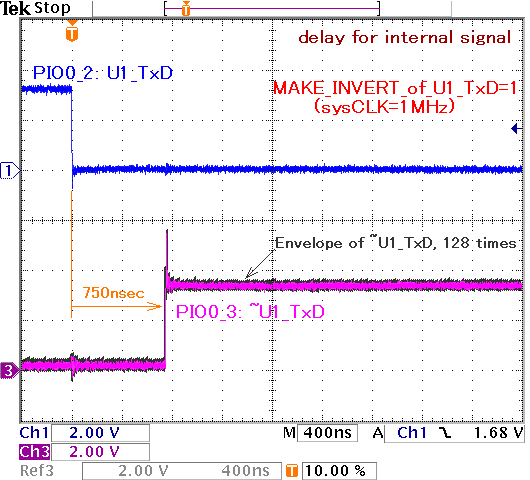

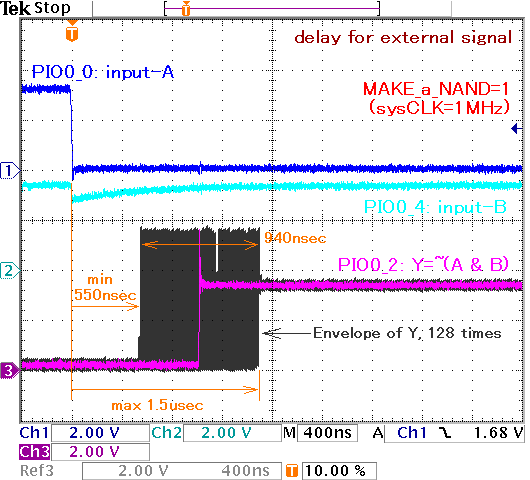

- * - * -It seems that, at least, final output signal RXEV / BMAT is synced by sysCLK.

It can be used to processing input signals.

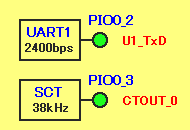

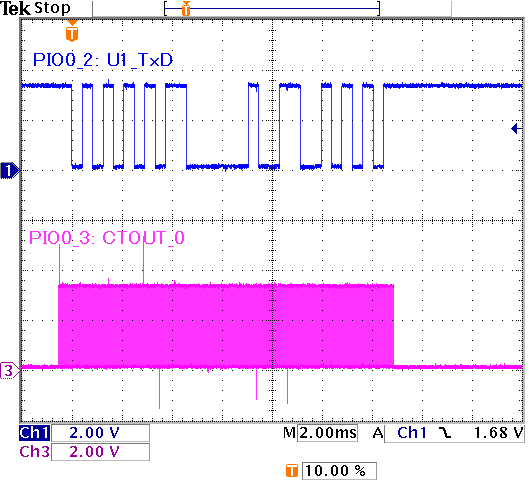

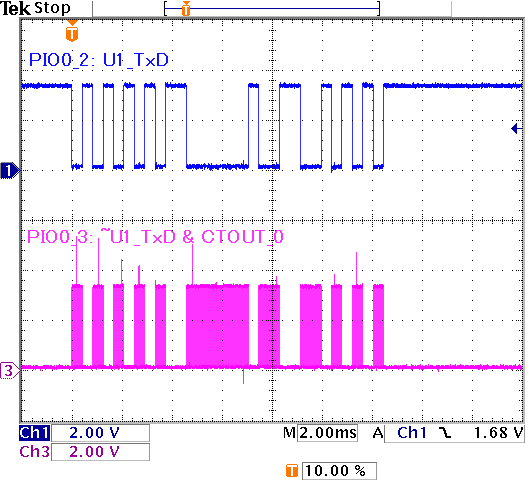

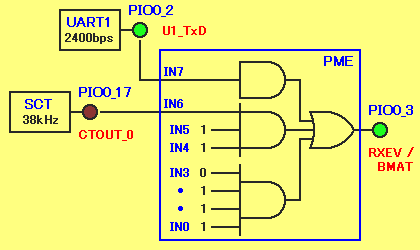

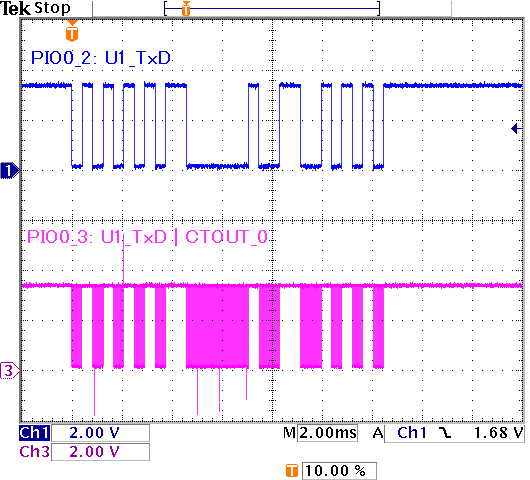

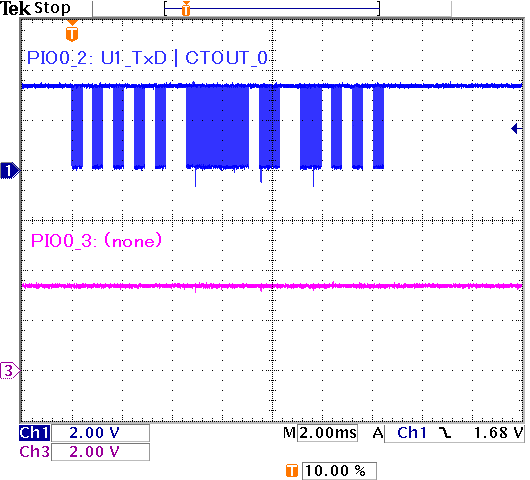

I had to make some UART logger, had to sense 2 UART wire TxD and RxD.

But dip8 LPC810 has only 2 UART module, and the one is necessary to connect host PC.

I added (negative logic OR) 2 UART signals TxD / RxD by PME.

As for UART logger, yes it is not enough to sense full-duplex communications, but in my case, it is enough because half-duplex.