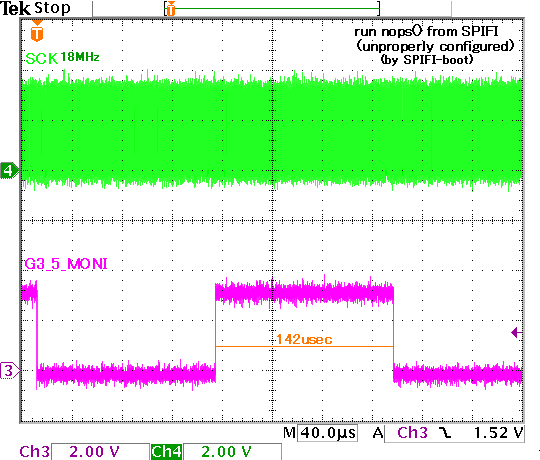

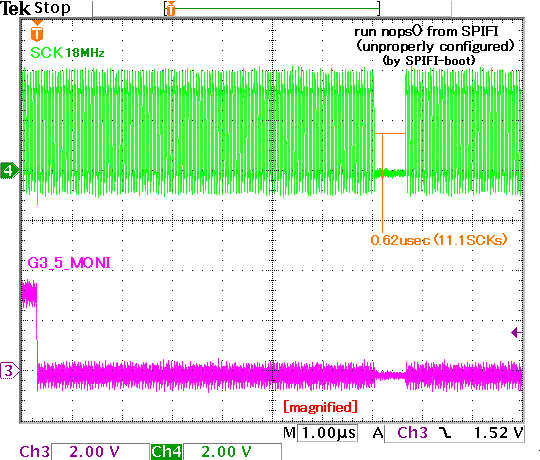

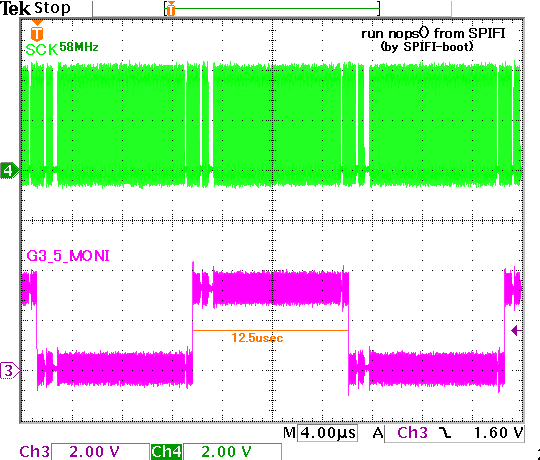

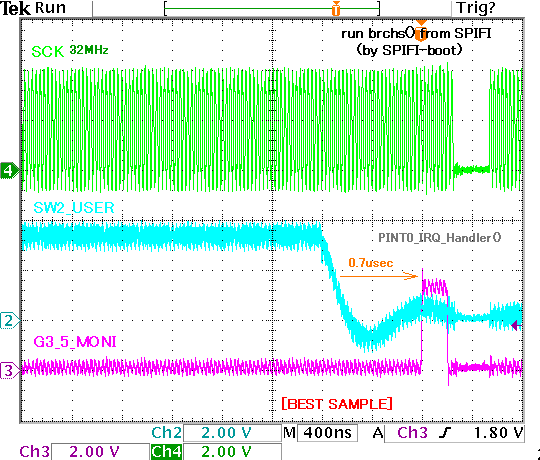

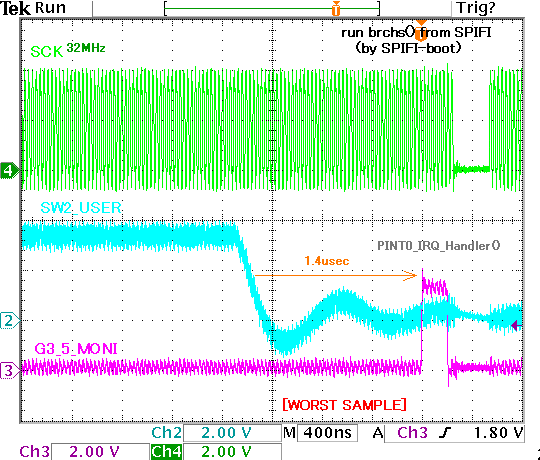

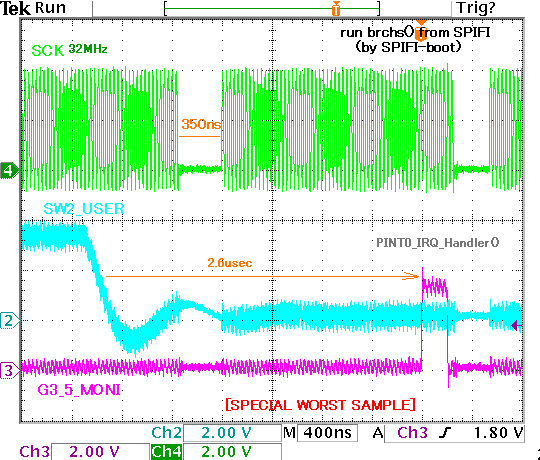

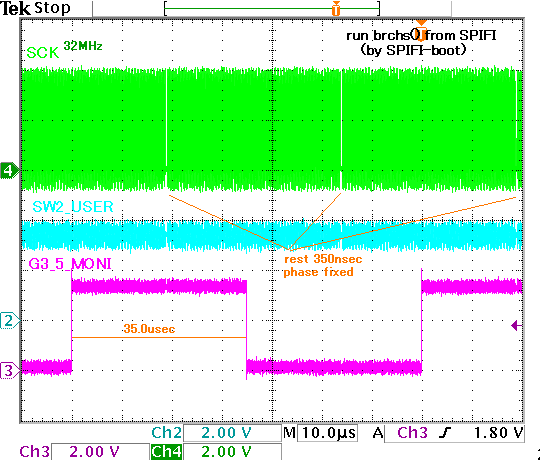

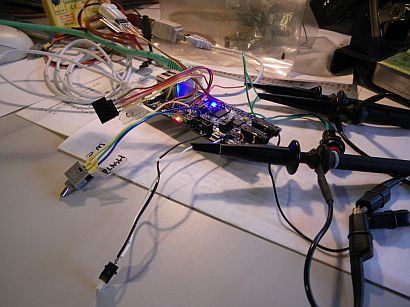

- tested by LPC1830-Xplorer. (chip revision A) (S25FL032P)

-

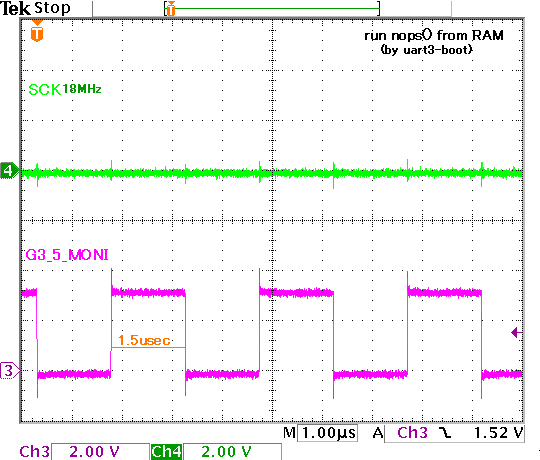

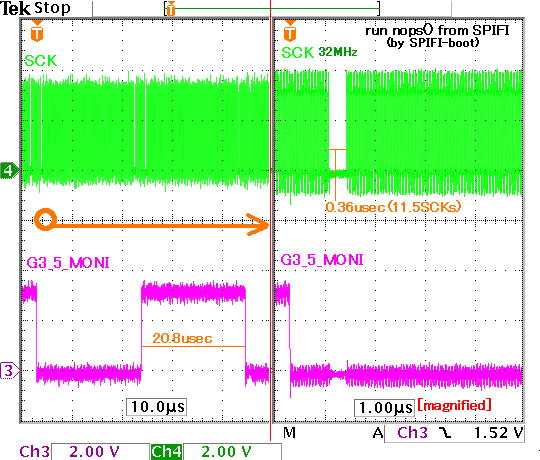

the program is run on 0x1000_0000, by uart3-boot.

(see main.c for action detail, other files are in test-spifi/* of minimon-011.zip) - the core runs at 96MHz, and SPIFI interface clock is 18MHz.

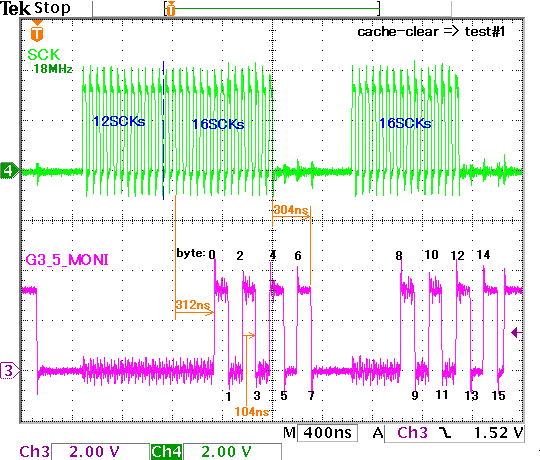

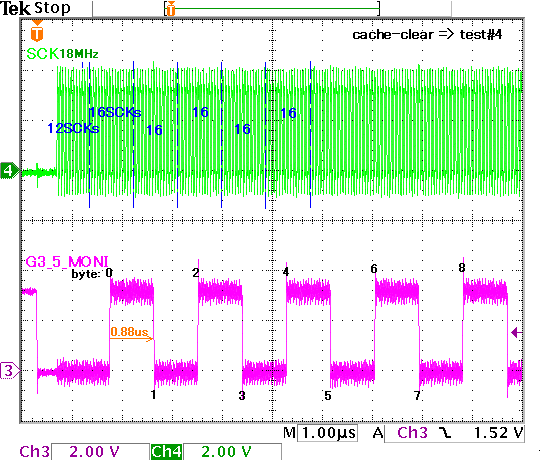

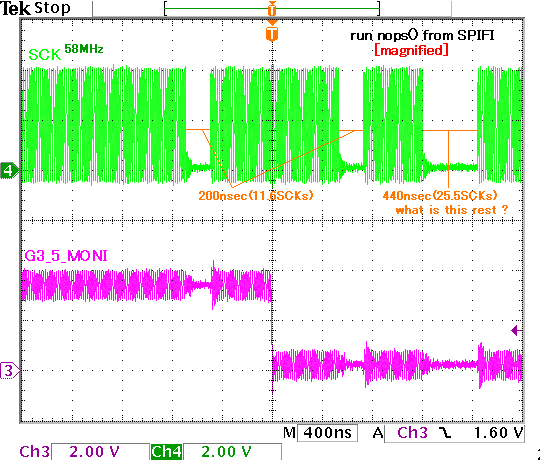

001: continuous byte read ('1')

- 8bit * 8bytes / 16SCK = 4bit/SCK, quad mode may be effective.

- command and address may be sent by first 12SCKs.

- continuous command/address may be omitted by sequential access.

- it takes about 5 or 6 SCKs to data fed is ready. (including delay to GPIO)

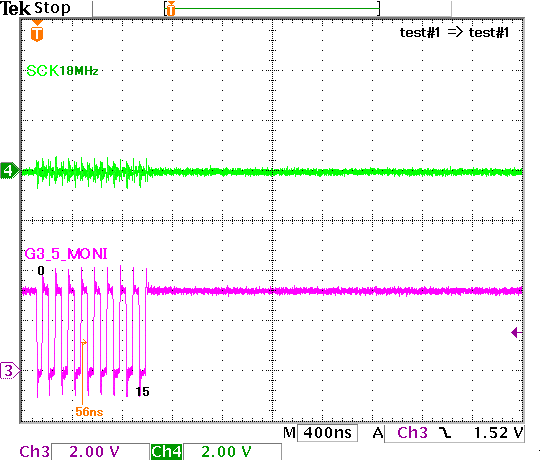

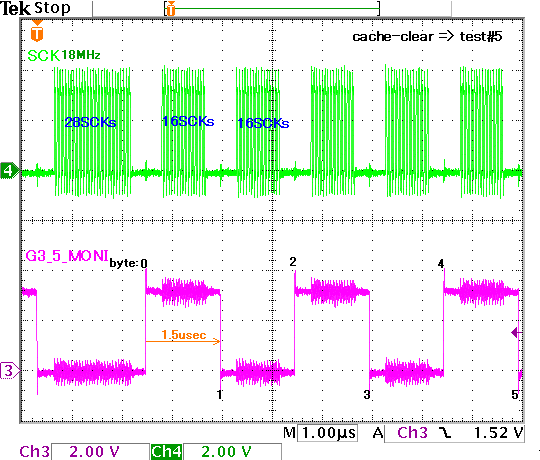

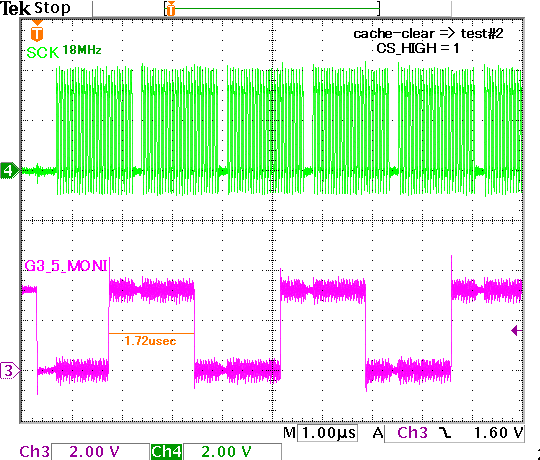

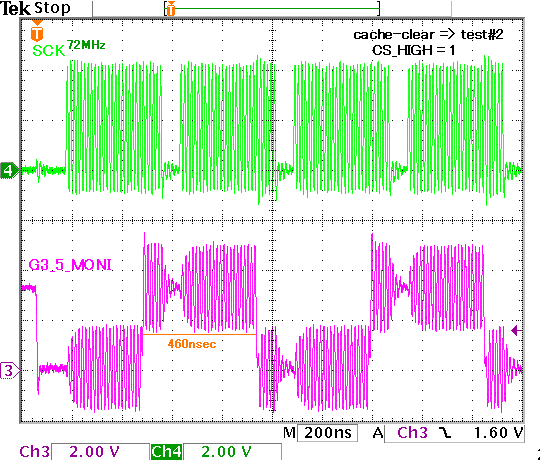

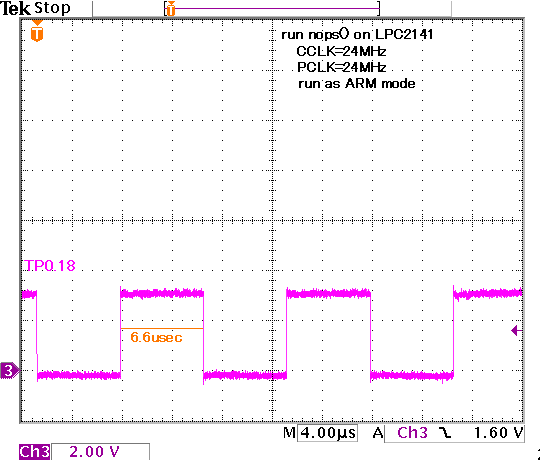

002: repeat "continuous byte read" ('1')

- there is no access when repeated, some cache may be.

( 56nsec / 96MHz = 5.3clks ... almost no loss )

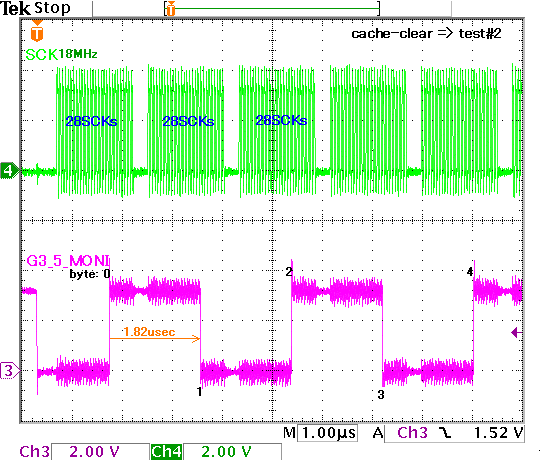

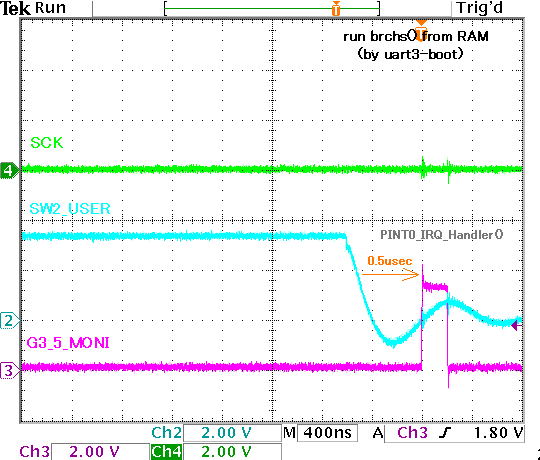

003,004: separated byte read ('2', '3')

- command/address may be sent everytime when non-continuous.

- read request for SPIFI may be always done by 8byte boundary.

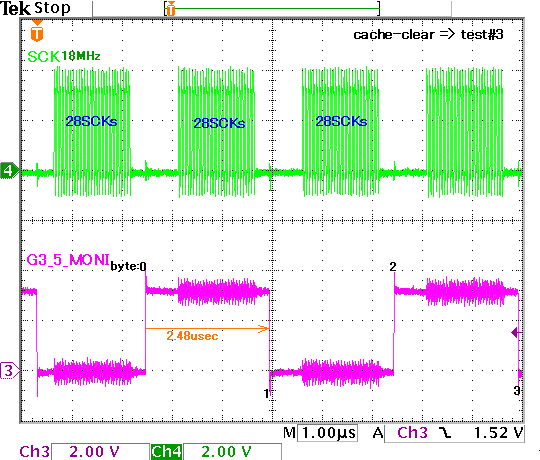

005,006: byte in continuous boundary read ('4', '5')

- access for SPIFI is continuos when it is the best case, but will this occur when instruction read ?