| jump to: more more2 magicFlash slow SPIFI-flash mF more mF more2 pt-msc drv_spifi ...... |

| J-doc3 J-doc2 examine SPIFI-flash J-doc1 external pins chip revision |

/* * initial bench to try LPC1830-Xplorer * by uratan! 2012.10.10 * revised 2014.1.11 */

jump to: more more2 magicFlash slow SPIFI-flash mF more mF more2 pt-msc drv_spifi ...... J-doc3 J-doc2 examine SPIFI-flash J-doc1 external pins chip revision

First release

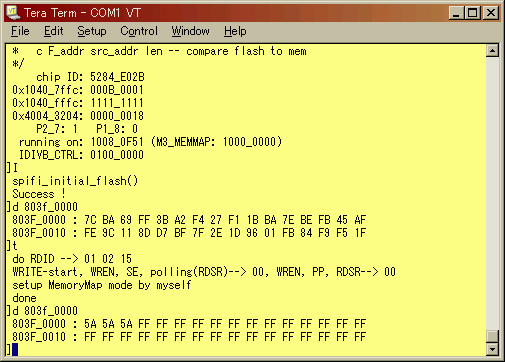

With USART3-boot, monitor which can dump/edit memories will run.

minimon-001.zip

ouch! once more

Second release

With USART3-boot, monitor which can dump/edit memories, erase/write SPIFI-flash will run.

minimon-004.zip

spifi.c: line 209: ", stat" is missing... ihex.c: line 203: "ext_addr <<= 16;" is missing...

Third release

With USART3-boot, monitor which can dump/edit memories, erase/write SPIFI-flash will run.

Also, write this binary and boot from SPIFI-flash, this will be a 2nd boot-loader which see P1_8 to run monitor (P1_8=low) or run user-program at 0x10_0000 on SPIFI-flash (P1_8=open).

minimon-008.zip

Final release

With USART3-boot, fake ISP which emulates LPC1857 will run first. With sending '/' instead of '?', you can enter monitor which can dump/edit memories, erase/write SPIFI-flash.

Also, write this binary and boot from SPIFI-flash, this will be a 2nd boot-loader which see P1_8 to run ISP/monitor (P1_8=low) or run user-program at 0x10_0000 on SPIFI-flash (P1_8=open).

minimon-010.zip

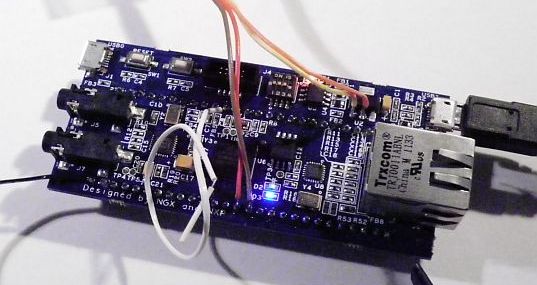

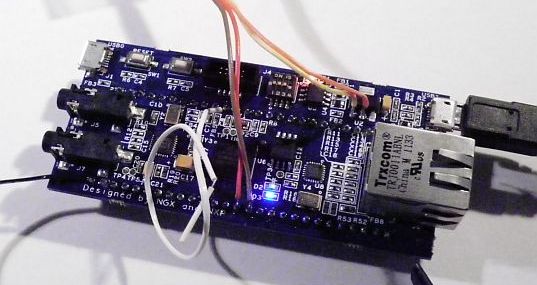

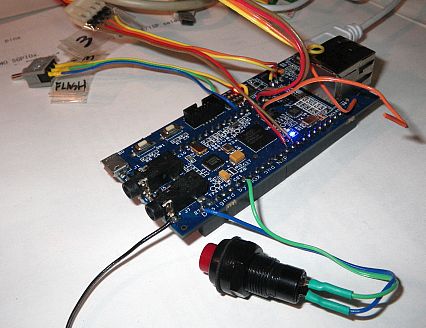

connection

It seems that this patch is effective to avoid "SPIFI-boot vs reset-twice" problem.

You shall control it at your user-program layer, not at magicFlash boot-loader, because your user-program can be run without magicFlash.

I have bought another Xplorer and confirmed it. This pristine Xplorer toggles RUN and FREEZE just as the errata, does not run on slow mode. Let's forget. (2013.1.29)

*** ..\minimon-010\main.c Wed Oct 24 11:10:09 2012 --- main.c Sun Nov 11 18:51:08 2012 *************** *** 23,28 **** --- 23,33 ---- */ /* + * reset myself to retry if SPIFI is configured unproperly + */ + #define ENABLE_SPIFI_RETRY 1 + + /* * fake_ISP() or minimon(), which mode to run first when P1_8 is low. */ #define RUN_MINIMON_FIRST 0 *************** *** 78,85 **** /* * detect boot src, and boot request for me */ ! boot_from_spifi = (M3_MEMMAP == 0x80000000) ? 1 : 0; spifi_boot_requested = (GPIO1_PIN & SW_MyBSEL_G1_1) ? 1 : 0; /* * do NOT boot from my-boot-area when uart-boot or other --- 83,104 ---- /* * detect boot src, and boot request for me */ ! boot_from_spifi = (M3_MEMMAP >= 0x80000000) ? 1 : 0; spifi_boot_requested = (GPIO1_PIN & SW_MyBSEL_G1_1) ? 1 : 0; + + #if ENABLE_SPIFI_RETRY + /* + * confirm SPIFI initialization properness if booted from SPIFI + */ + if(boot_from_spifi) { + if(IDIVB_CTRL != 0x09000820) { + /* reset myself */ + RESET_CTRL0 = RES0_CORE_RST; /* 1clk -> auto-clear */ + while(1) + ; + } + } + #endif /* ENABLE_SPIFI_RETRY */ /* * do NOT boot from my-boot-area when uart-boot or other

* the document is translated ! 0eREADME.txt

* also has small small changes, compare by yourself plz.

minimon-011.zip

* handling for 02 record of intel-HEX file is added.

* try to port PeripheralTest. (only USB1(VCOM) and Ether)

(get lpc1830_Xplorer_Keil.zip from here)

* test-spifi2/ added, for interrupt vs SPIFI-flash examination

* and so on, compare by yourself plz.

minimon-012.zip

* I had ported CMSIS 'Examples/USBDEV/Usb_MassStoraga/' by corner-cutting.

(get CMSIS - lpc18xx-2012-12-11.zip from here) (==> *re_dist* (61MB))

* also has a console to control interrupt function settings.

see 00README.txt in detail.

==> pt-msc-005.zip

* Try to access SPIFI-flash through SPIFI interface without spifi_drv_M3.lib

==> t-drv_spifi.zip